概 述

底部填充包封材料起初应用于提高早期氧化铝(Al2O3)基材的倒装芯片的可靠性。在芯片最外围的焊点易疲劳而导致芯片功能失效。相对较小的硅片和基材间的热膨胀差异是芯片在经受热循环时产生这种问题的根源。这样,热循环的温度范围及循环的次数就决定了芯片的使用寿命。在芯片和基板间填充可固化的包封材料,可以很好地把热膨胀差异带来的集中于焊点周围的应力分散到整个芯片所覆盖的范围。

随着引入环氧材料作为倒装芯片的基材,底部填充材料的研发大大地加快了。为了延缓焊点的应力疲劳,较大的基材和芯片硅片材料间的热膨胀差异使得底部填充剂的应用成为必然。而在底部填充材料和芯片接合界面的分层及底部填充剂中的空洞是触发许多芯片产生问题的根本原因之一。本篇将要讨论的是减少底部填充剂中的空洞的一些方法。

毛细流动型的底部填充材料

这类底部填充材料是一种低粘度的液体,利用毛细作用润湿元件和基板并填充其间的缝隙,将焊点包封起来。为了产生毛细作用,填充剂需要应用在接近芯片的边缘的地方。较低的粘度和良好的润湿性能都是促使快速而完好地包封住焊点及满足一些其他特性的必要条件。应用这种毛细流动型的底部填充材料通常需要一些专门设计的设备,以达到足够高的精确性,良好的可重复性,及大规模生产的要求。基本上,点胶设备必须能重复地将预定量的填充剂点在元件边缘,连续作业。为了加快毛细流动,基板的预热一般作为第二个要求。胶水的固化通常使用带有传送带的回流炉或者烘箱。

设计适合底部填充工艺

的元件包封

合适的芯片包封设计可以避免许多底部填充的问题。首先来看看裸芯片的设计。均匀分布锡球的设计最容易获得完好的底部填充效果。在接近芯片中央的锡球周围密集或交叉布线都增加了产生空洞的可能。由于边缘的焊球最容易受杂质影响而且难于检查,在设计时尽可能避免把焊球布在距方型芯片边缘200m以内。焊盘的间距也尽可能拉大,以增大焊球直径从而产生较大的待填充的间隙。

不幸的是,裸芯片的设计通常难以充分考虑到工艺的可行性。焊球的设计往往取决于线路及其本身规则。在这种情况下,良好的基板的设计可以帮助减少或消除许多的隐患,达到包封芯片焊点或者获得期望的可靠性的目的。以下是一些简单的裸芯片基材设计的指引:

● 所有的半通孔需要填平而后表面覆盖阻焊膜。开放的半通孔可能产生空洞。

● 阻焊膜须覆盖除焊球对应焊盘外的所有的金属基底。

● 减少弯曲;保证一致的金属基底和阻焊膜。

● 尽可能消除沟渠状的阻焊膜开窗以确保一致性的流动。阻焊膜的一致,平整将确保没有细小的间隙容纳空气或者助焊剂的残留,而这些都是产生空洞的根源。

● 减少焊球周围的暴露的基底材料,配合好阻焊膜的尺寸公差。否则容易产生不一致的润湿效果。

● 减少对应焊球的焊盘的可焊接面积,从而增加间隙,配合贴片偏差和阻焊膜公差。

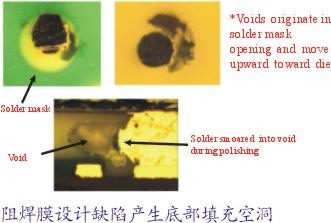

下面的照片是由于阻焊膜的缺陷造成空洞的示例。

底部填充前的准备

最近对底部填充剂粘接性能的研究证实了清洁度对于元件可靠性的巨大影响。特别地,不能够忽视助焊剂残留对底部填充剂的影响。所有的助焊剂都留有化学的残留物,这依赖于其类别和回流的条件状况。这些残留可能与填充材料不兼容而阻碍胶水与芯片及基板形成可靠的粘接。甚至于一些被称为免洗的,低残留的助焊剂配方有时确能产生很大的影响。

助焊剂的残留影响可靠性的方式可以分成两类。一种显而易见的方式是阻碍了填充剂对于芯片和基板间间隙的填充。底部填充材料不能润湿带有不兼容残留或表面能较高的表面。

不一致的润湿通常使得填充材料在毛细流动和回流固化过程中产生空洞。这很容易在焊点周围助焊剂集中的地方观察到。有时在这些位置会集中较大块的残留。因为芯片下的间隙都可能有残留分布,所以不一致的润湿产生的空洞可能存在于芯片下面的任何地方。

助焊剂第二种影响可靠性的方式是减少界面的粘接性能。少量的不阻碍包封的残留可能降低填充剂对于相邻表面的粘接力,特别是对于芯片的粘接。通常在焊球或者芯片的边缘受压而产生异常地分层就是这个原因引起。

清洗:

清洗工艺被大多电子组装生产厂商所排斥。只有一些特别地封装,医疗器械,汽车电子等对芯片可靠性要求高地应用才会利用清洗确保产品可靠性。通常需要昂贵地设备投入,不在线操作。

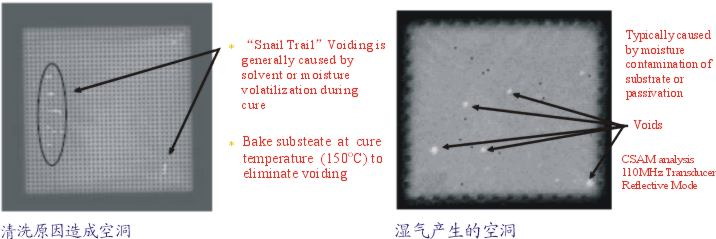

有效地清洗整个芯片下的表面和完整地除去清洗处理液是最大的挑战。特别对于较大的芯片,较小的间隙而言更加困难。实践证明了要得到好的效果需要具体了解关于清洗设备,清洗液,芯片情况,助焊剂类型,使用助焊剂工艺,回流条件的信息。附图显示了助焊剂的残留和清洗处理液残留引起的空洞情况。完全地清除清洗液可能需要在做底部填充前对产品进行一定地烘烤。

多数的厂商使用Plasma清洗工艺以确保底部填充剂一致的流动性及对不同性质表面的粘接性。Plasma清洗间隙较深处的的效果对于胶水的粘接力的影响还不确定。

除去吸附的湿气:

有机的封装材料表面吸附的湿气是导致胶水固化后产生空洞的主要原因。芯片及线路板的表面都可能附着湿气。空洞经常是产生可靠性问题的根源,特别是当它存在于两个邻近的锡球之间时。分层也源于有空洞的地方。在回流过程中,焊锡可能流入空洞或是分层的区域。当空洞延伸到邻近的焊球就直接导致短路。

对于所有的环氧材料,能量的扩散和平衡使其产生从周围环境吸附湿气的作用力。在胶固化时升高温度使得大部分湿气挥发出去。水汽会从阻焊膜的开窗及多孔的基体表面进入填充材料。这样,蒸汽压挤开部分胶水,当其固化后就留下了空洞。

在做填充工艺前烘烤芯片可以除去湿气产生的空洞。对1mm厚的基材而言,典型的条件是在125C,烘烤2小时。不同的封装形式需要的时间也不同。如果烘烤的温度升高,相应地时间可以缩短。底部填充工艺应在烘烤后的两小时内开始进行。下面的示图是湿气产生的空洞。

一些生产工艺在应用底部填充之前需要一次或多次的回流。在这种情况下,事先的烘烤工艺可以忽略。这也适用于底部填充工艺是在基板从密封的包装取出两小时内操作,假设在封入包装前已进行过烘烤。材料在应用前须按照要求做好充分的检查。

如果预先烘烤在整个工艺中很难实现,则须考虑不在线烘烤基板而后暂时保存于密封的,保养得当的干燥箱中待用。可以通过试验得到允许的最长的储存时间。不建议不确定储存条件,因为吸附湿气的作用随时都在进行的。另外,由于干燥箱并不能除去湿气,不建议基板不经烘烤就放入干燥箱保存。

注意任何沸点低于填充剂固化温度的附着于芯片基板表面的杂质都可能产生空洞。水是最普通的污染物。基板生产中的一些残留的挥发物可能在正常的预先烘烤工艺中没有完全除去。通常很难把这类空洞同湿气形成的空洞区分开来。这种挥发物可能需要更高温度的预烘烤或者通过两个阶段的填充剂固化过程来消除空洞的产生。

点胶设备

点胶机

点胶主要的目的是将底部填充剂分散到芯片和基板的间隙中,以提高整个产品的可靠性。这通常需要利用胶水的毛细流动作用实现对基板和裸芯片间的间隙的完全的填充。

许多公司为底部填充剂的应用提供了很好的产品。最复杂的设备是完全自动化的,具有传送基板的装置,多个阶段的预热装置和移动的点胶头。建议厂商选择适合自身工艺,预算和未来规划的设备。

泵的技术

所有的点胶机都依赖液压泵来衡量胶水的用量。泵的技术在准确性,重复性,成本上都有很大差异。由于填充剂在芯片四周的围边大小和空洞都和胶水的用量有很大关系,所以控制好填充剂的用量尤为重要。

时间压力泵是最简单和便宜的,但在重复性方面很差。它是依靠施加于胶管顶部的气压来把胶水压出。压力是通过接在胶管后面的气管来施加。胶水的流速可以粗略地认为和压力成比例。流速受到很多其他因素的影响,包括针内径的大小,胶管中胶水的多少和胶水本身的粘度。而粘度本身又和温度,以及回温后在使用温度下放置的时间有关。附图为四种不同的底部填充剂点胶流速与时间的关系。除了A之外的其他材料的流速呈现随时间有规律的降低。对这三种材料来说,为了保证一致的点胶量,需要不断调整时间和压力,特别是D,它的开罐寿命很短。

较低的准确性和重复性限制了时间-压力这种点胶设备在大规模生产中的应用。当可以做到持续的控制点胶量的条件下,它可以适用在较小规模或者零散的生产中。滴胶是这类泵的普遍的问题。控制好点胶时的气压对于解决这个问题是很关键的。

旋转螺纹或者是螺纹驱动泵在点胶表现上有了很大的改进。填充剂的用量是通过螺纹的步进来控制的。它仍需要气压来推动螺纹挤出胶水。流速取决于螺纹的转速和填充剂的粘度。粘度同样和温度及胶水开罐的寿命有关。下图示意了螺丝泵输出的一致的胶水流速。

旋转的螺纹泵是应用底部填充剂的很好的选择。良好的重复性可以通过周期性的检测流速获得。滴胶的情况也会在低粘度的产品上出现。

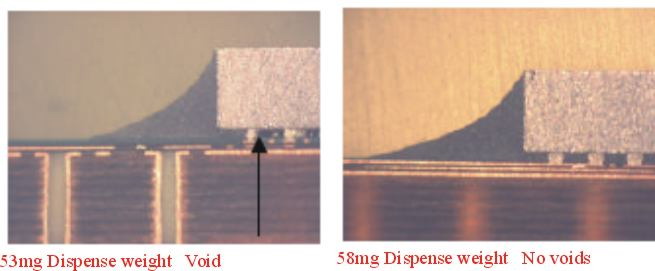

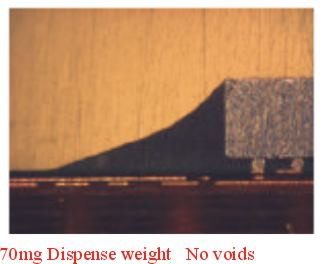

下面的切片照片显示了底部填充剂用量不足引起空洞的情况。在这项试验中,对130个倒装芯片做底部填充,填充剂的用量从50-70mg不等。19个样品查出有空洞形成,而其中16个芯片的充胶量低于53mg。

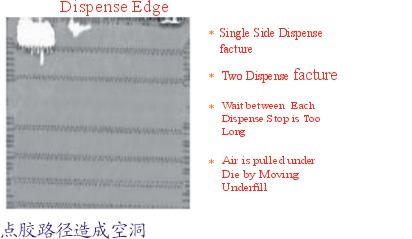

胶水用量不足产生的空洞是由于沿点胶边缘的填充剂过少在胶水流到另一边之前不能完成对芯片完整的填充,这样就会包裹一些气泡在里面。下面的照片显示的都是点胶路径对面的芯片边缘位置。

活塞型或线性正位移的泵是应用底部填充最可靠的方式,可以获得很好的准确性和重复性。其原理是利用一个步进电机驱动一个活塞在盛有填充剂的圆筒状的容器中运动。因为活塞的位移及圆筒容器的设计很精确,这样点胶量就可以控制得很准确。如果操作得当,标准的点胶偏差小于2%,只需很少的监测就能获得稳定的表现。 只要设备的状况正常,滴胶的问题通常不会出现。

只要设备的状况正常,滴胶的问题通常不会出现。

点胶

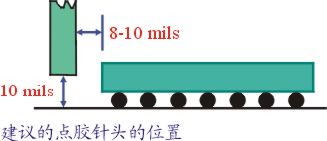

为了使足够的填充剂充满整个芯片和基板的间隙,同时减少流到芯片外围的胶水的量,点胶针头在点胶时位置的控制非常重要。也就是说点胶针头离芯片的距离和距基板的高度都是很关键的影响因素。这些会因元件的大小,流动速度,和距离基板的基准位置的不同而不同。典型的设定范围如下图所示:

控制底部填充剂的流动

底部加热:

底部加热有效地帮助填充剂充满间隙。一般而言,胶水的流动速度和润湿力会随温度升高而提高。另外,杂质和残留溶解度也随温度升高而增加,这就减少了空洞的产生。

底部填充剂的供应商在提供产品时都会建议产品最佳的预热温度,通常是在80-100C。在这个温度下,胶水可以达到最佳的流动速度和润湿能力,同时使胶体呈现胶凝状态前填充满芯片和基板的间隙。对于较大的芯片可能会使用较高底部预热温度以提高胶水的流动速度和对各种杂质的溶解能力。

点胶路径:

点胶路径:

在点胶时。点胶的路径指针头画出的两维的路线。有些路径会被时间和点胶位置分割开。点胶的路径直接由点胶设备来控制。对于手工的时间-压力点胶操作来说,则取决于操作者。选择路径的目标是花费较短的流动及点胶时间,得到没有空洞的完好的填充效果,并在芯片周围有适合的胶水附着,呈斜坡形状。这样,芯片实现理想的包封,提升了产品的可靠性,工艺过程的时间也能得到控制。

给芯片设计点胶路径时,应充分考虑到点胶的时间,点胶后胶水流动的形态,和是否在路径对角的芯片边缘有合适的成型。对于不能在边缘自成型的胶水,或者当成型不均匀时,需要增加一些工艺时间来达到理想的效果。

最简单的点胶样式是在芯片的一角或某一边的中点点一个点。这种样式会在点胶处的边缘有较多的残胶。它适合于小的芯片,或者在胶水流动时较容易包裹进空气的应用。对较大的芯片来说,这种方式胶水填满间隙需要的时间很长。

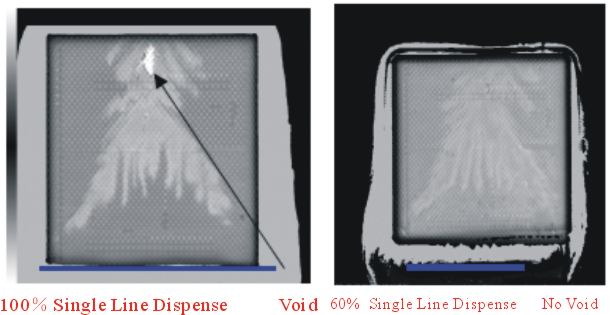

直线型的点胶,或称“I”型点胶,适用在需要在芯片边缘形成较小成型的应用。填充时,须注意控制不要有空气卷入。在芯片较长的一边点胶可以减少流动的时间。点胶的路线长度一般是芯片边长的50%-125%。较长的路线能帮助减少芯片边缘的胶水成型,但增加了在点胶位置对边包裹住一些气泡的可能性。

“L”型的点胶路径是沿芯片相邻的两边点胶。这种方式可以得到较小的点胶边缘位置的胶水成型,同时胶水的流动时间也最短。需要说明的是短的路径确保产生没有空洞的完好的填充。点胶设备应小心设定避免点胶针头在点胶时碰到芯片的边缘。在芯片下可以观察到一块小区域,胶水在那里汇合,边缘的胶水成型很小。这个汇合处并不影响产品的可靠性,除非这里有过多的不相容的残留集结。

最初点胶样式应该使用充足的胶量完全填充芯片和基板的间隙。如果出现在点胶一侧的胶水成型太大的情况,可以利用在同一路径多次点胶的方式来改进。理想的点胶路径需要在点胶的时间和芯片边缘胶水成型之间权衡。芯片边缘的胶水太少会使容纳空气的空间增加。下图就是这类空洞的示例。

目前市场上有许多可以在芯片边缘自成型的填充剂产品。这意味着胶水流动的前端可以在点胶位置的对面一侧的芯片边缘形成理想的斜坡,胶水可以爬升到芯片厚度的50%以上的位置。这样,填充间隙后的围边步骤也可以省去。反之,如果使用的填充剂不能在边缘处自成型,就需要增加在除点胶路径之外的芯片边缘围边的工序。举例来说,“I”型的点胶路径需要增加“U”型的围边步骤。而“L”型的点胶则需要另一个“L”型的围边过程。

对其他的点胶参数的巧妙调整也可以控制点胶量。要均匀的点胶,需要点胶泵在点胶前启动。胶水可以有足够的时间在针头移动前接触到基板的表面。同时,保持好针头与芯片的距离,以免碰到芯片,使胶水粘到芯片的上表面。通常这个距离要不小于250m。控制好针头的高度可以帮助针头在芯片边缘均一地划线。这个高度是指针尖平面到基板的距离,建议达到250m,特别是在胶水容易拉丝的时候。当点胶速度很快时,需要再提高针头高度以保证有足够的点胶空间。此时,胶水的流速很快,针头会有较多的胶水残留。

总结

空洞是由于引入了空气,其他的气体,溶剂或水而产生。为了消除空洞,必须要了解清楚它的来源。而空洞的位置,形状实际上提供了很多线索,可以帮助我们使用有效的方法去消除它。

感谢

Kathy Lewis and Kathy Costello for their efforts in imaging test parts. Michael Todd for his input in identifying sources of voiding.

参考资料

[1]“Process Defects and Analysis of Low Cost Flip Chip Processing”; Daniel Baldwin, Mike Tsai and Paul Houston; 2ND APEX Conference, SMEMA, January 14 18, 2001; San Diego, California, AT5-1.

[2].“Flip Chip Underfill Flow Characteristics and Predictions”; P. Fine, B. Cobb, and L. Nguyen; 49th ECTC, June 1-4, 1999, page 791

[3]. “Evaluation of Underfill in Flip Chip and BGA on PC Boards Using 3V Reconstruction and Through Transmission Analysis”; Janet E. Semmens; 5th Annual Pan Pacific Microelectronics Symposium; January 25 27, 2000, page 233

[4]“Fast Underfill Process for Large to Small Flip Chips”;Alec Babiarz, Horatio Quinones and Robert Ciardella; 6th Annual Pan Pacific Microelectronics Symposium; February 13 16, 2001 Page 55.

[5]“Manufacturability Issues of Flip Chip on Laminate Assemblies”Jing Qi, R. Wayne Johnson, Erin Yeager, Mark Konarski, Todd Dooly, Z. Andrew Szezepaniak, Larry Crane; IMAPS International Journal Microcircuits and Electronic Packaging, Volume 22, 3rd Quarter, 1999, page 270.

[6]“Effects of Post-Reflow Cleaning Proce sses On the Performance of Flip-chip Devices”Michael Todd and Mike Bixenman; 1st Annual APEX Conference, March 12 14, 2000. P-AP6/3